主要职责

中国科学院贯彻落实党中央关于科技创新的方针政策和决策部署,在履行职责过程中坚持党中央对科技工作的集中统一领导。主要职责是:

一、开展使命导向的自然科学领域基础研究,承担国家重大基础研究、应用基础研究、前沿交叉共性技术研究和引领性颠覆性技术研究任务,打造原始创新策源地。 更多+

院况简介

中国科学院是国家科学技术界最高学术机构、国家科学技术思想库,自然科学基础研究与高技术综合研究的国家战略科技力量。

1949年,伴随着新中国的诞生,中国科学院成立。建院70余年来,中国科学院时刻牢记使命,与科学共进,与祖国同行,以国家富强、人民幸福为己任,人才辈出,硕果累累,为我国科技进步、经济社会发展和国家安全作出了不可替代的重要贡献。 更多+

院领导集体

科技奖励

科技期刊

科技专项

科研进展/ 更多

工作动态/ 更多

工作动态/ 更多

中国科学院学部

中国科学院院部

语音播报

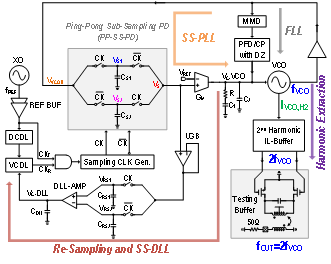

5.5G/6G无线通信技术的迭代演进及下一代串行接口向更高传输速率突破,对毫米波本振时钟抖动性能提出了更严苛的要求。亚采样锁相环凭借其高鉴相增益的优势,成为低抖动时钟芯片的主流解决方案,但仍面临挑战。

中国科学院微电子研究所与清华大学合作,提出双边沿乒乓亚采样锁相环架构。该架构同时利用参考时钟的上升沿与下降沿,实现了参考频率的等效倍频,解决了传统亚采样锁相环在环路带宽、带内相位噪声与参考杂散之间存在的设计折衷难题。团队还提出高功率与面积效率的注入锁定缓冲器方案,该结构在高效提取振荡器二次谐波的同时能够实现谐波整形,降低了锁相环带外相位噪声。

基于上述两种技术,团队采用65nm CMOS工艺设计了一款K波段锁相环时钟芯片,输出频率覆盖22.4GHz至25.6GHz,整体功耗低于18mW,RMS积分抖动优于50fs,其抖动—功耗优值达到−254dB以下。

相关研究成果在线发表在《IEEE固态电路学报》(IEEE Journal of Solid-State Circuits)上。研究工作得到国家自然科学基金的支持。

乒乓亚采样锁相环电路结构

扫一扫在手机打开当前页

© 1996 - 中国科学院 版权所有 京ICP备05002857号-1  京公网安备110402500047号 网站标识码bm48000002

京公网安备110402500047号 网站标识码bm48000002

地址:北京市西城区三里河路52号 邮编:100864

电话: 86 10 68597114(总机) 86 10 68597289(总值班室)