主要职责

中国科学院贯彻落实党中央关于科技创新的方针政策和决策部署,在履行职责过程中坚持党中央对科技工作的集中统一领导。主要职责是:

一、开展使命导向的自然科学领域基础研究,承担国家重大基础研究、应用基础研究、前沿交叉共性技术研究和引领性颠覆性技术研究任务,打造原始创新策源地。 更多+

院况简介

中国科学院是国家科学技术界最高学术机构、国家科学技术思想库,自然科学基础研究与高技术综合研究的国家战略科技力量。

1949年,伴随着新中国的诞生,中国科学院成立。建院70余年来,中国科学院时刻牢记使命,与科学共进,与祖国同行,以国家富强、人民幸福为己任,人才辈出,硕果累累,为我国科技进步、经济社会发展和国家安全作出了不可替代的重要贡献。 更多+

院领导集体

科技奖励

科技期刊

科技专项

科研进展/ 更多

工作动态/ 更多

工作动态/ 更多

中国科学院学部

中国科学院院部

语音播报

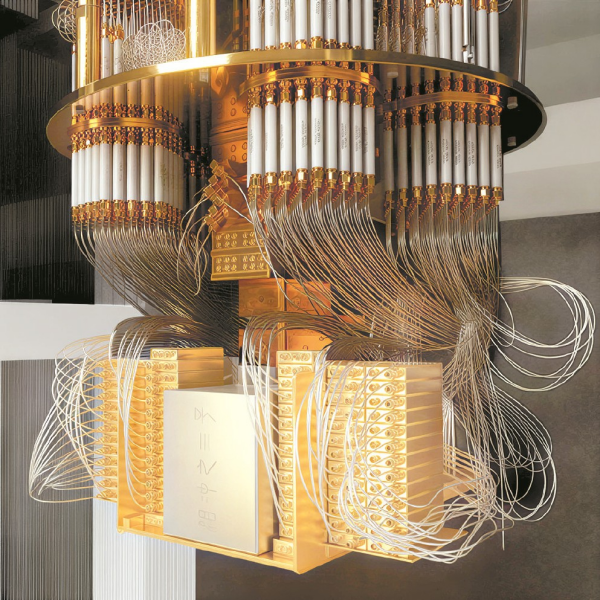

超导量子计算原型机“祖冲之三号”。(图源:中国科学技术大学上海研究院)

量子纠错是实现大规模量子计算的关键基础,近日我国科学家在这一领域重大突破。记者昨天从中国科学技术大学获悉,该校潘建伟、朱晓波、彭承志、陈福升等领衔的研究团队,基于超导量子处理器“祖冲之3.2号”,在码距为7的表面码上达到“低于阈值,越纠越对”的量子纠错关键里程碑。

这一成果的取得,是基于该团队独创的“全微波控制”全新路径,其纠错效率和可扩展性均优于美国谷歌公司之前的方案。12月22日,该成果以封面论文和“编辑推荐”形式发表于国际权威学术期刊《物理评论快报》,美国物理学会《物理》栏目对此进行了专题报道。

对量子计算机而言,量子比特极易受环境干扰而产生错误。因此,通用量子计算必须借助量子纠错来抑制这类错误,以满足大规模集成要求。目前,量子纠错最成熟的方案之一是“表面码”,它将多个物理量子比特编码成一个逻辑量子比特以抵御干扰。虽然从原理上说,随着物理比特数目(即码距)的增加,逻辑比特的错误率将不断降低,但在实践中,该方案却面临悖论——为纠错而引入的额外量子比特和量子门操作,本身也会带来更多噪声源和错误通道;一旦物理量子比特的原始错误率过高,纠错的努力就会显得“得不偿失”,淹没在新增的错误中,导致“越纠越错”。

目前,全球量子纠错都把研究焦点放在如何降低物理比特的错误水平,特别是要抑制其中一种“泄漏错误”,最终使整体操控精度突破“纠错阈值”。只有跨越这一严苛的阈值,量子纠错才能产生正向净收益,做到“越纠越对”。

中国科大超导量子计算研究团队在国际上较早布局量子纠错研究,2022年他们率先实现了码距为3的表面码逻辑量子比特,首次验证了表面码方案的可行性。此次,团队基于107比特的“祖冲之3.2号”量子处理器,实现了码距为7的表面码逻辑比特。实验数据显示,其逻辑错误率随码距增加而显著下降,错误抑制因子达1.4,证明系统已工作在纠错阈值之下,成功达到“越纠越对”的目标,而这被公认为量子计算系统从实验室原型到实用化的关键分水岭。

更具里程碑意义的是,中国科大方案还展现出了独特的竞争优势。事实上,谷歌公司曾于今年2月利用其“垂柳”处理器,在码距为7的表面码上实现了低于阈值的逻辑比特。然而,该技术路线基于直流脉冲量子态泄漏抑制方法,不仅对量子处理器的芯片架构施加了较多约束,而且扩展性差,随着量子比特数的增加,该技术路线需要在极低温环境下进行复杂布线,硬件资源开销极大。

中国科大团队则独辟蹊径,依托“祖冲之3.2号”处理器本身所具备的高精度单双比特门操作、长相干时间等优异性能,提出并成功实践了全新的“全微波量子态泄漏抑制架构”,具有天然的频分复用特性,在硬件效率和扩展性上较谷歌路线具有显著优势,从而为未来构建百万比特级量子计算机提供了一种更具优势的解决方案。

(原载于《文汇报》 2025-12-24 03版)

© 1996 - 中国科学院 版权所有 京ICP备05002857号-1  京公网安备110402500047号 网站标识码bm48000002

京公网安备110402500047号 网站标识码bm48000002

地址:北京市西城区三里河路52号 邮编:100864

电话: 86 10 68597114(总机) 86 10 68597289(总值班室)